- 制造厂商:AD

- 产品类别:定时IC和时钟

- 技术类目:时钟产生器件

- 功能描述:带JESD204B接口的高性能、3.2 GHz、14路输出抖动衰减器

- (AD代理渠道,提供当日发货、严格的质量标准,满足您的目标价格)

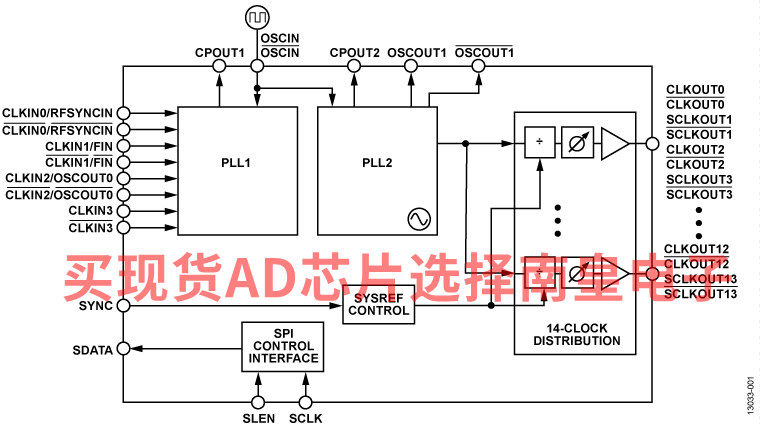

HMC7044是一款高性能双环路整数N分频抖动衰减器,能够选择参考并生成超低相位噪声的频率,支持配有并行或串行(JESD204B型)接口的高速数据转换器。 HMC7044具有两个可通过SPI选择的整数模式PLL和交叠的片内VCO,调谐范围分别达2.5 GHz和3 GHz。 该器件旨在满足GSM和LTE基站设计的要求,并通过多种时钟管理和分配特性来简化基带和无线电卡时钟树的设计。 HMC7044提供14路低噪声且可配置的输出,可以灵活地与许多不同器件接口,包括数据转换器、现场可编程门阵列(FPGA)和混频器本振(LO)。

HMC7044的DCLK和SYSREF时钟输出可配置来支持CML、LVDS、LVPECL和LVCMOS等信号标准,不同的偏置设置则可抵消变化的板插入损耗。

应用- JESD204B时钟产生

- 蜂窝基础设施(多载波GSM、LTE、W-CDMA)

- 数据转换器时钟

- 微波基带卡

- 相控阵参考分配

- 超低rms抖动: 典型值:44 fs(12 kHz至20 MHz,2457.6 MHz)

- 噪底: −156 dBc/Hz (2457.6 MHz)

- 低相位噪声: −141.7 dBc/Hz(800 kHz时,983.04 MHz输出)

- PLL2最多提供14路LVDS、LVPECL或CML型器件时钟(DCLK)

- CLKOUTx/CLKOUTx和SCLKOUTx/SCLKOUTx最高频率达3200 MHz

- JESD204B兼容系统参考(SYSREF)脉冲

- 25 ps模拟延迟和½ VCO周期数字延迟,14个时钟输出通道各自都能对延迟进行编程

- 相位噪声与功耗的关系可通过SPI编程

- SYSREF有效中断可简化JESD204B同步

- 窄带、双核VCO

- 最多2个缓冲压控振荡器(VCXO)输出

- LVDS、LVPECL、CMOS和CML模式下最多4个输入时钟

- 频率保持模式可保持输出频率

- 信号丢失(LOS)检测和无中断参考切换

- 4个GPIO报警/状态指示器,可确定系统健康程度

- 支持最高6000 MHz的外部VCO输入

- 片内稳压器提供出色的PSRR

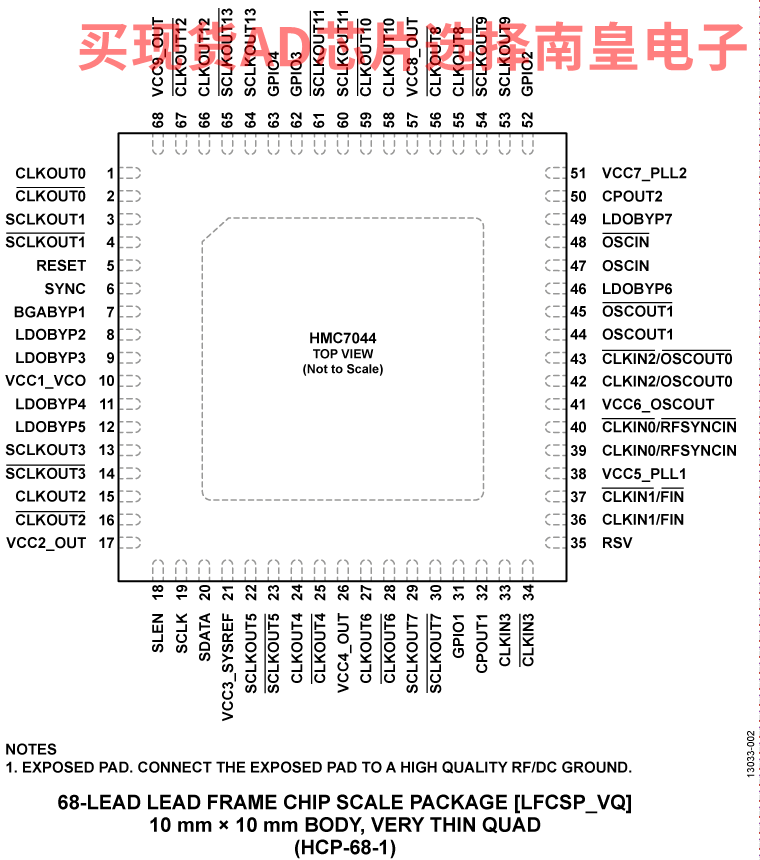

- 68引脚、10 mm × 10 mm LFCSP封装

HMC7044LP10BE,封装:68-Lead QFN (10mm x 10mm w/ EP),包装形式及数量:Cut Tape,500,工作温度:-40 to 85C,AD官网报价:19.72(100-499个)

HMC7044LP10BETR,封装:68-Lead QFN (10mm x 10mm w/ EP),包装形式及数量:卷带,500,工作温度:-40 to 85C,AD官网报价:19.72(100-499个)

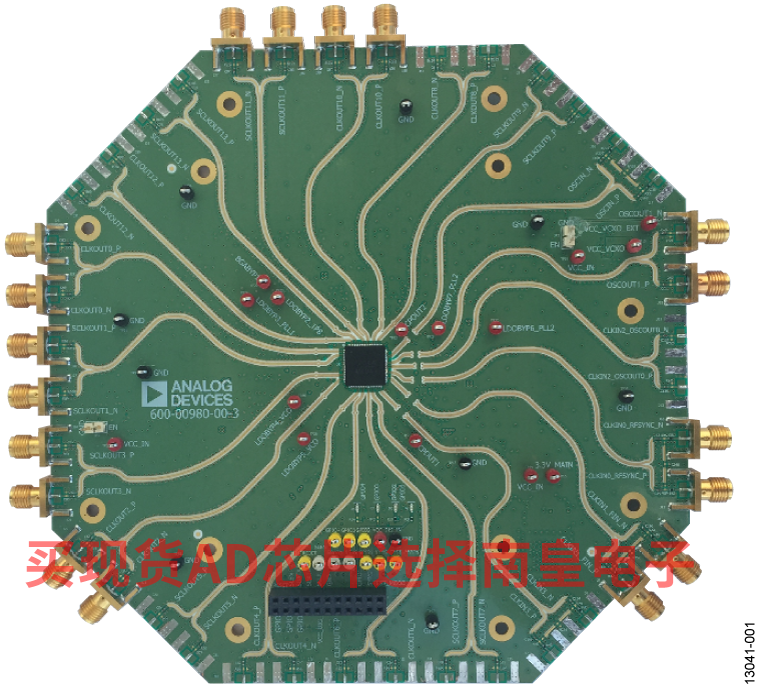

EVAL-HMC7044:HMC7044评估套件

HMC7044可满足多载波GSM和LTE基站设计的要求,并通过多种时钟管理和分配特性来简化基带和射频无线上网卡时钟树的设计。 基站设计人员借助窄带配置第一PLL环路来限制外部VCXO,同时配合HMC7044的高性能双环内核使主系统参考时钟(如CPRI源)的输入抖动性能衰减,从而利用宽带第二PLL产生低相位噪声和高频时钟,以驱动数据转换器采样时钟输入。

EK1HMC7044LP10B评估板是一款紧凑、易于使用的平台,可用来评估HMC7044的全部特性。 该评估板上装有122.88 MHz VCXO以提供完整的解决方案。 评估板上的所有输入和输出均配置为差分形式。

该产品数据手册提供HMC7044的完整规格,使用评估板时应同时参考用户指南与数据手册。