- 制造厂商:AD

- 产品类别:锁相环(PLL)频率合成器和转换环路

- 技术类目:小数N分频PLL

- 功能描述:低相位噪声,快速解决6 GHz 锁相频率合成器

- (AD代理渠道,提供当日发货、严格的质量标准,满足您的目标价格)

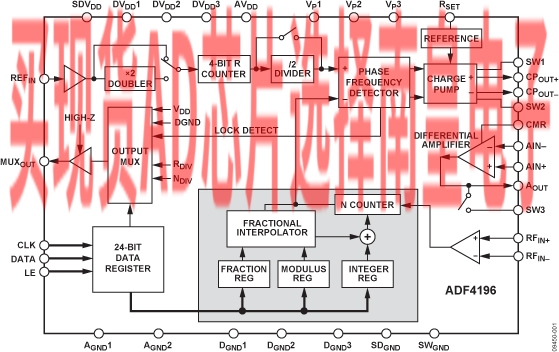

ADF4196由低噪声数字鉴频鉴相器(PFD)和精密差分电荷泵组成。还有一个差分放大器,用来将电荷泵的差分输出转换为外部电压控制振荡器(VCO)的单端电压。Σ-Δ型小数插值器与N分频器一起使用,能够实现可编程模数小数N分频。此外,4位参考(R)分频器和片内倍频器允许PFD输入端的参考信号(REFIN)频率为可选值。

如果频率合成器与外部环路滤波器和VCO一起使用,则可以实现完整的锁相环(PLL)。开关结构确保PLL能在GSM时隙保护期间内建立,而无需第二PLL及相关的隔离开关。与以前的乒乓式GSM PLL结构相比,这种结构能节省成本,降低复杂度,减小PCB面积,并减少屏蔽和特性测试工作。

应用

- GSM/EDGE基站

- PHS基站

- 脉冲多普勒雷达

- 仪器仪表和测试设备

- 波束形成/相控阵系统

- 快速建立小数N

分频PLL结构 - 单个PLL可取代乒乓式频率合成器

- 在5 μs内完成整个GSM频段上的跳频,相位建立时间低于20 µs

- 相位误差:1度rms

(4 GHz RF输出) - 数字可编程输出相位

- 数字可编程输出相位

- RF输入范围最高可达6 GHz

- 三线式串行接口

- 片内低噪声差分放大器

- 相位噪声品质因数:–216 dBc/Hz

- 利用ADIsimPLL可实现环路滤波器设计

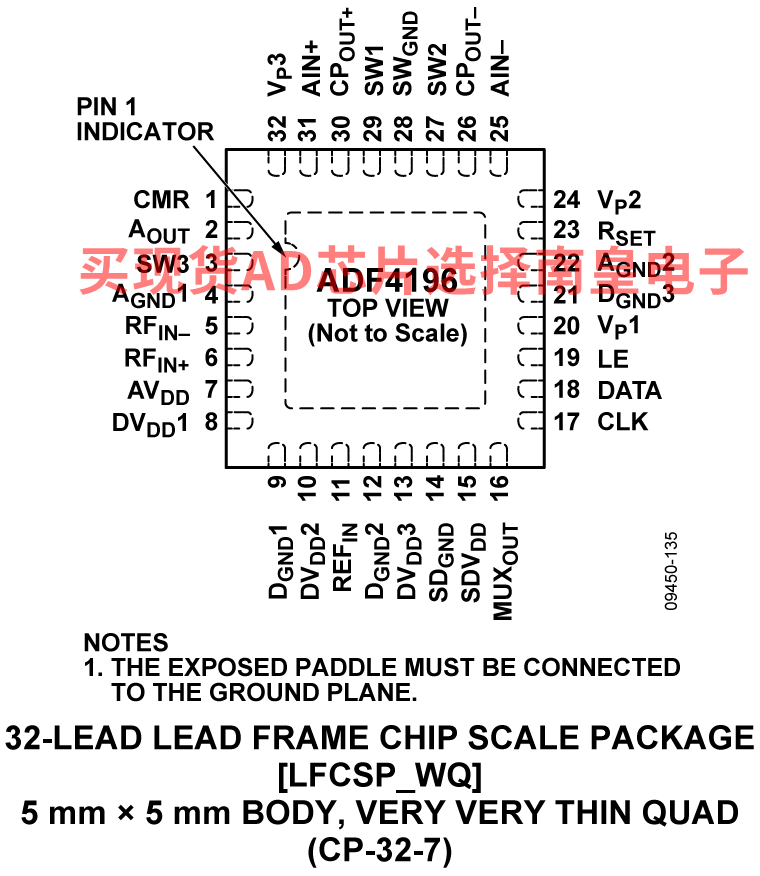

ADF4196BCPZ,封装:32-Lead LFCSP (5mm x 5mm w/ EP),包装形式及数量:托盘,490,工作温度:-40 to 85C,AD官网报价:12.13(100-499个);11.22(1000+个)

ADF4196BCPZ-RL7,封装:32-Lead LFCSP (5mm x 5mm w/ EP),包装形式及数量:卷带,1500,工作温度:-40 to 85C,AD官网报价:12.13(100-499个);11.22(1000+个)

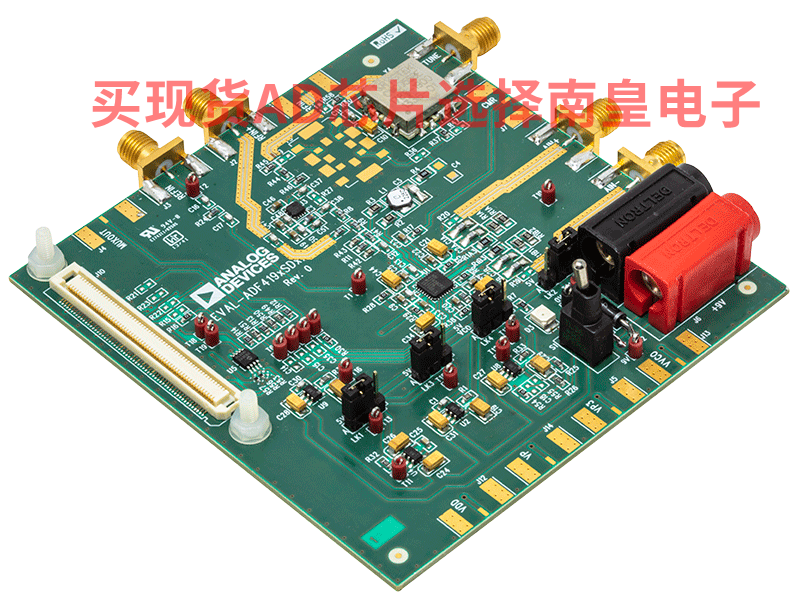

EVAL-ADF4196:ADF4196评估板

本页面包含用于评估ADF4196低相位噪声、快速建立6 GHz PLL频率合成器的评估板的订购信息。

注意:ADF4196芯片需要焊接至EVAL-ADF4193EBZ2电路板。

该评估板需使用SDP控制器版以连接PC。SDP控制器板通过USB 2.0连接至PC。评估板将连接至SDP控制器板。评估板无法直接连接至PC。在PC上运行的评估软件通过SDP控制器板与评估板通信。SDP控制器板在以下订购指南中单独列出(EVAL-SDP-CS1Z)。如果以前未购买过SDP控制器板,请购买该产品以确保获得完整的评估设置。