- 制造厂商:AD

- 产品类别:定时IC和时钟

- 技术类目:时钟产生器件

- 功能描述:带双路PLL、扩频和余量微调功能的时钟发生器

- (AD代理渠道,提供当日发货、严格的质量标准,满足您的目标价格)

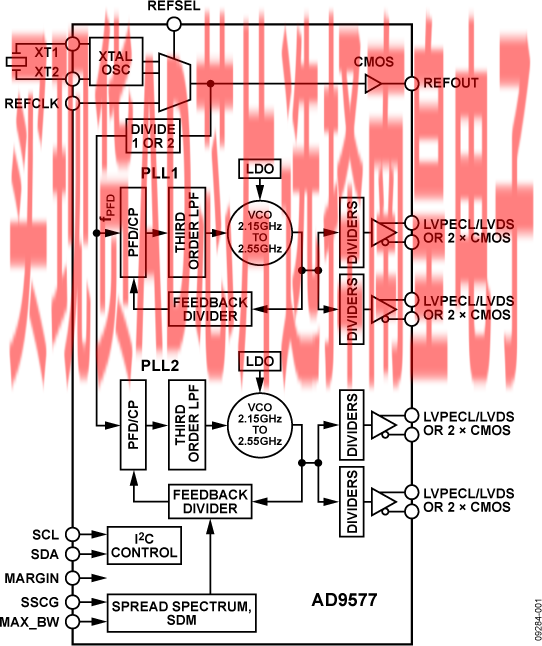

第一个整数N分频PLL部分(PLL1)由一个鉴频鉴相器(PFD)、一个电荷泵(CP)、一个低噪声电压控制振荡器(VCO)、一个可编程反馈分频器和两个独立可编程输出分频器组成。通过将外部晶振或基准时钟连接至REFCLK引脚,可将最高达637.5 MHz的频率同步至输入基准。针对所需输出速率,每个输出分频器和反馈分频器的比率可以是工厂设定或I2C 编程设定。

第二个小数N分频PLL(PLL2)内置一个可编程模块,可合成基准频率小数倍的VCO频率。针对所需输出速率(最高达637.5 MHz),每个输出分频器和反馈分频器的比率可以通过工厂编程设定。这个小数N分频PLL还可在整数N分频模式下工作以充分降低抖动。

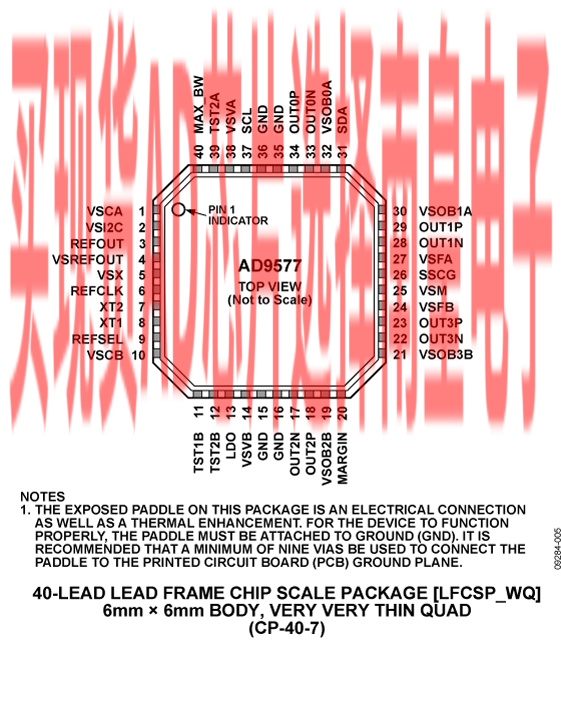

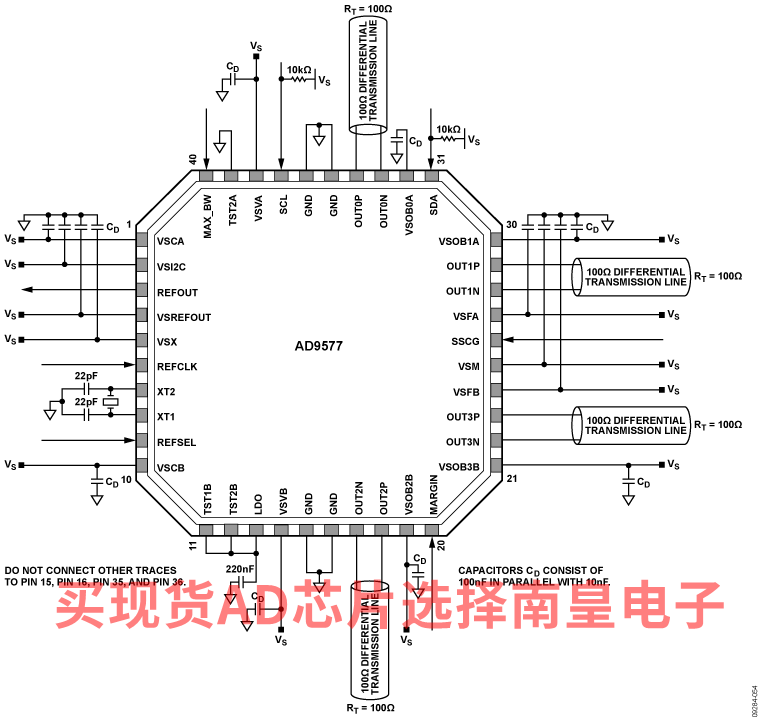

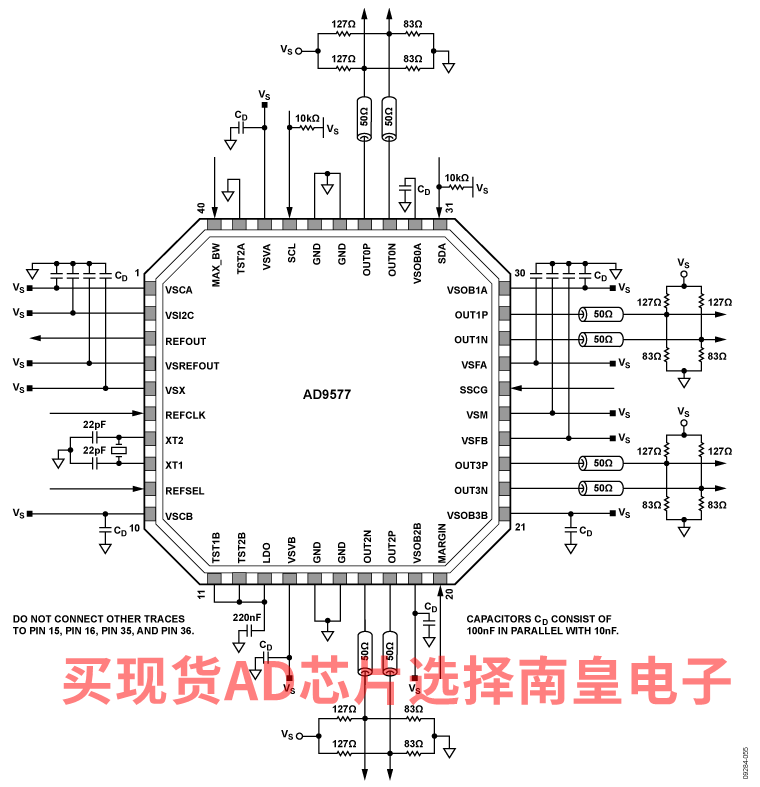

最多四个差分输出时钟信号可配置成LVPECL或LVDS信号传输格式。每个输出对也可配置用于最多八个CMOS输出。支持这类格式的组合。无需外部环路滤波器元件,从而节约了宝贵的设计时间和电路板空间。AD9577提供40引脚6 mm × 6 mm LFCSP封装,采用3.3 V单电源供电,工作温度范围为-40℃至+85°C。

应用

- 低抖动、低相位噪声多路输出时钟发生器,支持多种数据通信应用,包括以太网、光纤、SONET、SDH、PCI-e、SATA、PTN、OTN、ADC/DAC和数字视频。

- 扩频时钟

- 完全集成双路PLL/VCO内核

- 1个整数N分频和1个小数N分频PLL

- 连续频率范围:11.2 MHz至200 MHz

-- 提供200 MHz至637.5 MHz的大多数频率 - PLL1相位抖动

(12 kHz至20 MHz):

460 fs rms(典型值) - PLL2相位抖动(12 kHz至20 MHz)

- 整数N分频模式:470 fs rms(典型值)

- 小数N分频模式:660 fs rms(典型值)

- 输入晶体或基准时钟频率

- 扩频向下扩频 [0, −0.5]%

- 2引脚控制的频率分布图余量微调

- 集成环路滤波器

- 欲了解更多特性,请参考数据手册

AD9577BCPZ,封装:40-Lead LFCSP (6mm x 6mm w/ EP),包装形式及数量:托盘,490,工作温度:-40 to 85C,AD官网报价:6.12(100-499个);5.21(1000+个)

AD9577BCPZ-R7,封装:40-Lead LFCSP (6mm x 6mm w/ EP),包装形式及数量:卷带,750,工作温度:-40 to 85C,AD官网报价:6.12(100-499个);5.21(1000+个)

AD9577BCPZ-RL,封装:40-Lead LFCSP (6mm x 6mm w/ EP),包装形式及数量:卷带,2500,工作温度:-40 to 85C,AD官网报价:6.12(100-499个);5.21(1000+个)

EVAL-AD9577:AD9577 Evaluation Board

This page contains evaluation board documentation and ordering information for evaluating the AD9577.