- 制造厂商:AD

- 产品类别:定时IC和时钟

- 技术类目:时钟同步

- 功能描述:四通道输入、10路输出、双通道DPLL、1 pps同步器和抖动清除器

- (AD代理渠道,提供当日发货、严格的质量标准,满足您的目标价格)

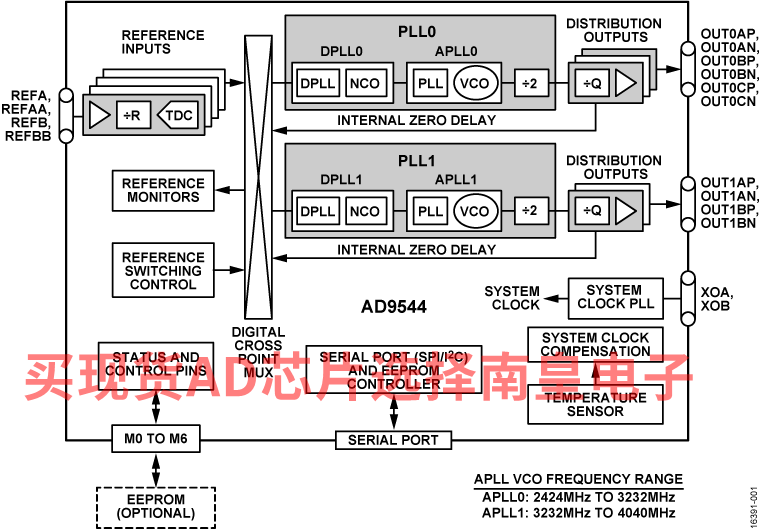

AD9544的10个时钟输出与最多四个输入基准电压源之一同步。数字锁相环(DPLL)可减少与外部基准电压源相关的时序抖动。借助数字控制环路和保持电路,即使所有参考输入都失效,也能持续产生低抖动输出信号。

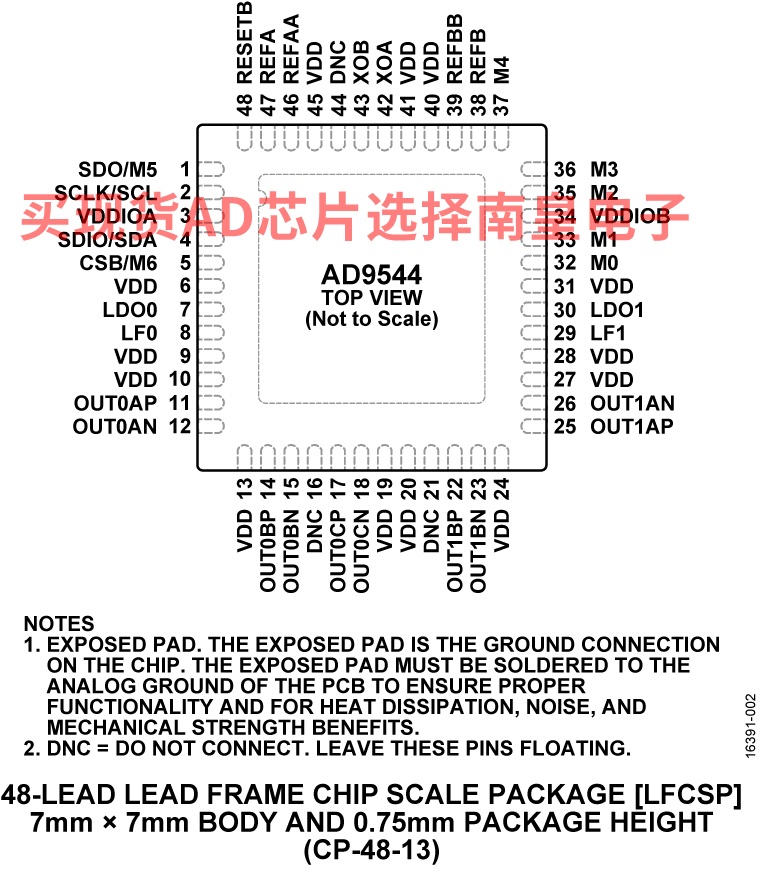

AD9544采用48引脚LFCSP (7 mm × 7 mm)封装,额定温度范围为?40°C至+85°C。

请注意,在整篇数据手册中,多功能引脚(如SDO/M5)由整个引脚名称或引脚的单个功能表示;例如M5即表示仅与此功能相关。

应用

- SyncE 和 GPS 同步和抖动清除

- 光传输网络(OTN)、SDH、宏和小型蜂窝基站

- 具有抖动净化功能的OTN映射/解映射

- 小基站时钟,包括基带和无线电

- Stratum 2、Stratum 3e 和 Stratum 3 保持、抖动清除及相位瞬态控制

- JESD204B 支持模数转换器 (ADC) 和数模转换器 (DAC) 时钟

- 有线基础设施

- 载波以太网

- 双路DPLL可同步1 Hz至750 MHz物理层时钟,提供高噪声参考源的频率转换以及抖动净化功能

- 符合ITU-T G.8262和Telcordia GR-253

- 支持Telcordia GR-1244、ITU-T G.812、G.813、G.823、G.824和G.825

- 连续频率监控和参考验证,频率偏差低至50 ppb

- 两个DPLL具有24位小数分频器和24位可编程模数

- 可编程数字环路滤波器带宽:10−4 Hz 至 1850 Hz

- 自动和手动保持和参考切换,提供零延迟、无中断或相位増建操作

- 基于优先级的可编程参考切换,支持手动、自动恢复和自动非恢复模式

- 5对时钟输出引脚,每对引脚均可用作差分LVDS/HCSL/CML或2路单端输出(1 Hz至500 MHz)

- 2个差分或4个单端输入基准电压源

- 交叉点多路复用器将参考输入互连至PLL

- 支持嵌入式(调制)输入/输出时钟信号

- 快速 DPLL 锁定模式

- 提供内部功能,结合晶振或晶体振荡器的低相位噪声以及TCXO或OCXO的频率稳定性和精度

- 为自主初始化提供外部EEPROM支持

- 1.8 V 单电源供电,具有内部调节特性

- 内置温度监控器/警报和温度补偿,可增强零延迟性能

AD9544BCPZ,封装:48-Lead LFCSP (7mm x 7mm x 0.85mm w/ EP),包装形式及数量:托盘,260,工作温度:-40 to 85C,AD官网报价:14.89(100-499个);12.58(1000+个)

AD9544BCPZ-REEL7,封装:48-Lead LFCSP (7mm x 7mm x 0.85mm w/ EP),包装形式及数量:卷带,750,工作温度:-40 to 85C,AD官网报价:14.89(100-499个);12.58(1000+个)

EVAL-AD9544:AD9544 评估板

AD9544 评估板是一款小巧且易于使用的平台,可用于评估 AD9544 双数字 PLL 和 1 PPS 同步器的所有功能。AD9544 提供高精度多输出时钟发生器功能以及两个片内去除信号抖动数字 PPL 内核。PLL0 和 PLL1 经过优化,适用于高性能同步时钟应用场合,例如 IEEE 1588 版本 2、同步以太网、OTN 和新一代无线基带协议。可通过串行端口控制对 PLL 进行完全配置,并且可通过外部 EEPROM 进行配置以完成上电配置。

AD9544 可输出最多 5 个差分时钟信号外加两个单端时钟,单端时钟由两个高性能数字 PLL 和两个高精度 NCO(数字控制的振荡器)驱动。评估板上可访问 12 个总输出和 4 个基准输入。

输出差分传输线对使用 50? 单端特性阻抗,并连接到标准边缘发射 SMA 连接器。AD9544/PCBZ 配备完全可配置的电源,用户可以在由降压开关稳压器或外部 LDO 直接供电时对 AD9544 进行评估。AD9544 评估板使用符合 RoHS 的 FR-4 材料。为方便起见,此处提供了 AD9544 数据手册中的详细信息。将此用户指南与 ADI 提供的数据手册一起使用。