- 制造厂商:AD

- 产品类别:高速ADC (负10MSPS)

- 技术类目:IF/RF接收器

- 功能描述:385 MHz BW IF分集接收机

- (AD代理渠道,提供当日发货、严格的质量标准,满足您的目标价格)

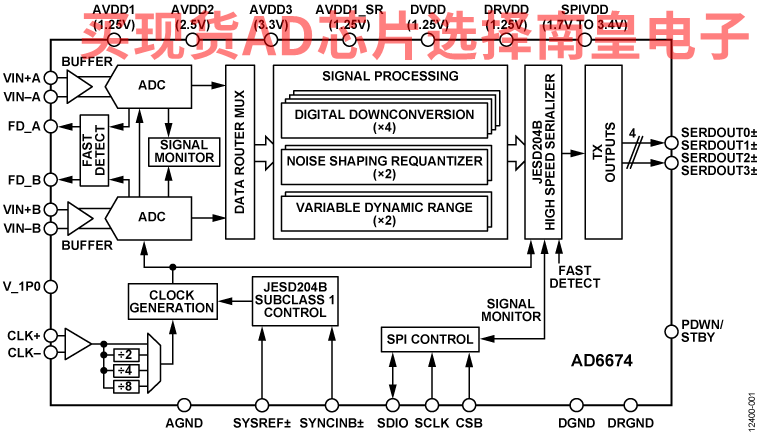

AD6674是一款385 MHz带宽混合信号中频(IF)接收器。内置双通道、14位1.0 GSPS/750 MSPS/500 MSPS模数转换器(ADC)和各种数字信号算法模块,包括四个宽带DDC、一个NSR和VDR监控。它具有片内缓冲器和采样保持电路,专门针对低功耗、小尺寸和易用性而设计。该产品设计支持通信应用,能够实现高达2 GHz的宽带宽模拟信号采样。AD6674针对宽输入带宽、高采样速率、出色的线性度和小封装低功耗而优化。

这款双通道ADC内核采用多级、差分流水线架构,并集成了输出纠错逻辑。每个ADC均具有宽带宽输入,支持用户可选的各种输入范围。集成基准电压源可简化设计考量。

应用

- 分集多频段、多模数字接收器 3G/4G、TD-SCDMA、W-CDMA、GSM、LTE、LTE-A

- DOCSIS 3.0 CMTS上游接收路径

- HFC 数字反向路径接收机

- JESD204B(子类1)编码串行数字输出

- 带内SFDR = 83 dBFS (340 MHz时,750 MSPS)

- 带内SNR = 66.7 dBFS (340 MHz时,750 MSPS)

- 750 MSPS 时每通道总功耗:1.4 W(默认设置)

- 噪声密度 = -153 dBFS/Hz (750 MSPS)

- 1.25 V、2.5 V和3.3 V 直流电源供电

- 灵活的输入范围

- AD6674-750和AD6674-1000

1.46 V p-p至1.94 V p-p(标称值1.70 V p-p) - AD6674-500

1.46 V p-p至2.06 V p-p(标称值2.06 V p-p)

- AD6674-750和AD6674-1000

- 95 dB通道隔离/串扰

- 幅度检测位支持实现高效自动增益控制(AGC)

- 噪声整形再量化器(NSR)选项支持主接收机功能

- 可变动态范围(VDR)选项支持数字预失真(DPD)功能

- 每通道集成 2 个宽带数字处理器

- 12 位数控振荡器(NCO),最多级联 4 个半带滤波器

- 差分时钟输入

- 整数时钟分频值:1、2、4或8

- 节能的关断模式

- 灵活的 JESD204B 通道配置

- 小信号扰动

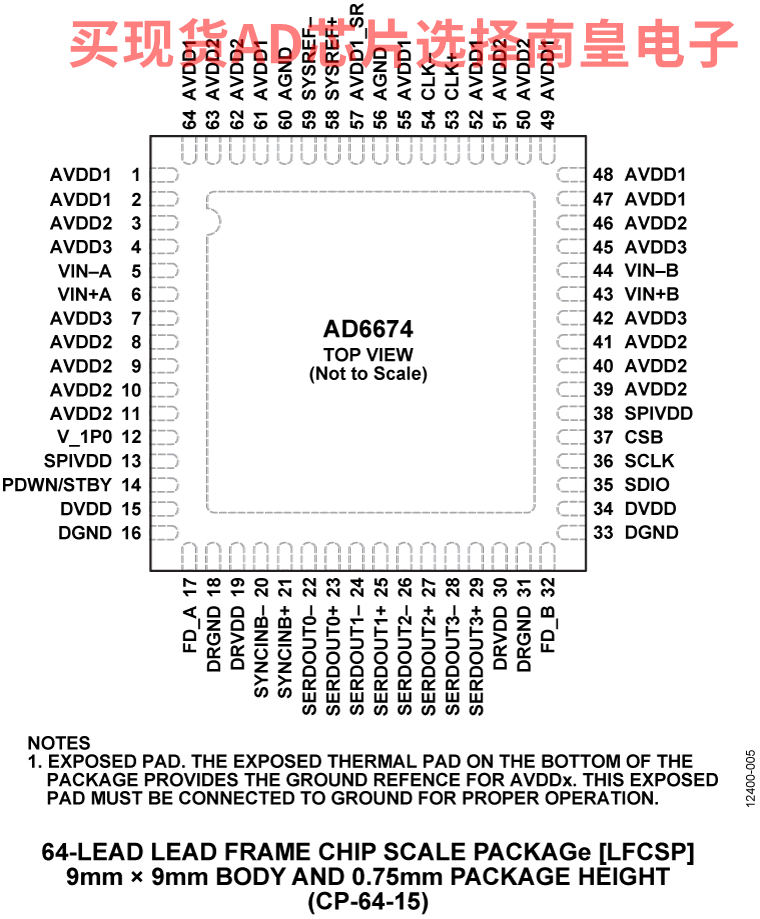

AD6674BCPZ-1000,封装:64-Lead LFCSP (9mm x 9mm w/ EP),包装形式及数量:托盘,260,工作温度:-40 to 85C,AD官网报价:825(100-499个);701.26(1000+个)

AD6674BCPZ-500,封装:64-Lead LFCSP (9mm x 9mm w/ EP),包装形式及数量:托盘,260,工作温度:-40 to 85C,AD官网报价:384(100-499个);326.40(1000+个)

AD6674BCPZ-750,封装:64-Lead LFCSP (9mm x 9mm w/ EP),包装形式及数量:托盘,260,工作温度:-40 to 85C,AD官网报价:522(100-499个);443.7(1000+个)

AD6674BCPZRL7-1000,封装:64-Lead LFCSP (9mm x 9mm w/ EP),包装形式及数量:卷带,750,工作温度:-40 to 85C,AD官网报价:825(100-499个);701.26(1000+个)

AD6674BCPZRL7-500,封装:64-Lead LFCSP (9mm x 9mm w/ EP),包装形式及数量:卷带,750,工作温度:-40 to 85C,AD官网报价:384(100-499个);326.40(1000+个)

AD6674BCPZRL7-750,封装:64-Lead LFCSP (9mm x 9mm w/ EP),包装形式及数量:卷带,750,工作温度:-40 to 85C,AD官网报价:522(100-499个);443.7(1000+个)

AD6674 EVALUATION BOARD:AD6674评估板

AD6674-1000EBZ评估板用于评估AD6674 385 MHz BW IF分集接收机。 本参考设计提供在各种模式和配置下运行该ADC所需的全部支持电路。 它设计为可直接与ADS7-V2EBZ的数据捕获卡进行接口,允许用户下载捕获的数据用于分析。 Visual Analog软件包用来与器件的硬件部分实现接口,允许用户下载捕获的数据并通过用户友好型图形界面进行分析。 同时,SPI控制器软件包也兼容硬件部分,可让用户使用AD6674的SPI可编程功能。用户指南 wiki 提供用于配置器件进行实验室性能评估的文档和说明。

AD6674数据手册提供了更多有关器件配置和性能的信息,在使用该评估板时应加以参考。 所有文档、Visual Analog软件以及SPI控制器均可在 高速ADC评估板 页面上找到。 欲了解更多信息,或有任何疑问,请发送电子邮件至highspeed.converters@analog.com设备要求

模拟信号源和抗混叠滤波器 采样时钟源 用于FPGA接收器的基准时钟源 运行Windows 7、XP或Vista的PC 建议使用USB 2.0端口(兼容USB 1.1) AD6674-1000EBZ评估板 ADS7-V2EBZ基于FPGA的数据采集套件 软件要求(U盘提供)

VisualAnalog (ftp://ftp.analog.com/pub/HSSP_SW/VisualAnalog/) SPI控制器 (ftp://ftp.analog.com/pub/adispi/A2DComponents/Install/ )

ADS7-V2EBZ:基于FPGA的数据采集套件

ADS7-V2评估板开发用于评估ADI公司采用JESD204B、位速率高达13.1 Gbps的高速ADC、DAC和收发器。以下列出的快速入门Wiki知识库在大体上概述了该平台情况。此外用独立章节逐个介绍了该板的每个用例(例如,ADS7-V2用于高速ADC评估)。ADS7-V2只能与指定的ADI公司评估板一同使用。ADS7-V2不可用作开发平台,也不支持独立运行。有关FPGA开发套件,请咨询Xilinx和其认可的代理商