- 制造厂商:AD

- 产品类别:高速ADC (负10MSPS)

- 技术类目:IF/RF接收器

- 功能描述:双通道中频接收机

- (AD代理渠道,提供当日发货、严格的质量标准,满足您的目标价格)

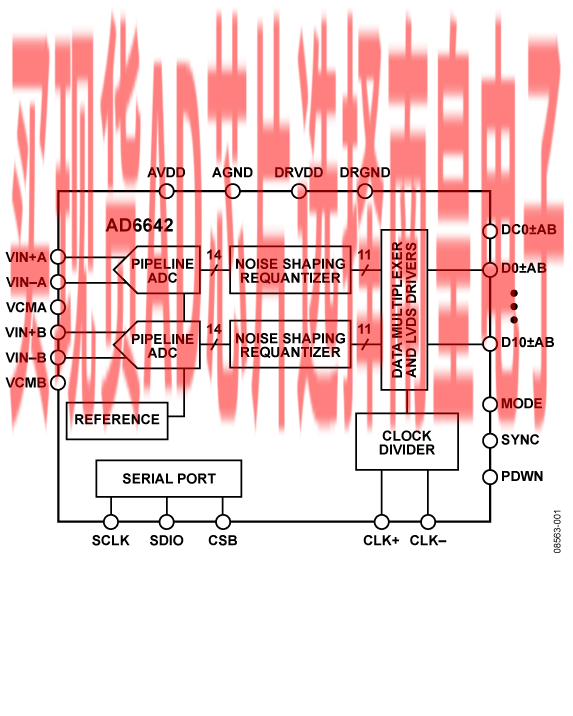

AD6642是一款11位、200 MSPS、双通道中频(IF)接收机,专门针对要求高动态范围性能、低功耗和小尺寸的电信应用中支持多通道系统而设计。

该器件包括两个高性能模数转换器(ADC)和噪声整形再量化器(NSR)数字模块。各ADC采用多级、差分流水线架构,并集成了输出纠错逻辑。ADC差分流水线的第一级包含一个宽带宽开关电容采样网络。集成基准电压源可简化设计。占空比稳定器(DCS)补偿ADC时钟占空比的波动,使转换器保持出色的性能。

各ADC的输出内部连接到NSR模块。集成NSR电路能够提高奈奎斯特带宽内较小频段的信噪比(SNR)性能。该器件支持两种不同的输出模式,通过外部MODE引脚或SPI可以选择输出模式。

如果使能NSR特性,则在处理ADC的输出时,AD6642可以在有限的部分奈奎斯特带宽内实现更高的SNR性能,同时保持11位输出分辨率。可以对NSR模块进行编程,以提供采样时钟22%或33%的带宽。例如,当采样时钟速率为185 MSPS时,在22%模式下,AD6642可以在40 MHz带宽内实现最高75.5 dBFS的SNR; 在33%模式下,它可以在60 MHz带宽内实现最高73.7 dBFS的SNR。

如果禁用NSR模块,则ADC数据直接以11位的分辨率提供给输出端。这种工作模式下,AD6642能够在整个奈奎斯特带宽内实现最高66.5 dBFS的SNR。因此,AD6642可以用于电信应用,例如要求更宽带宽的数字预失真观测路径。

经过数字信号处理后,多路复用输出数据路由至两个11位输出端口,最大数据速率为400 Mbps (DDR)。这些输出设置为1.8 V LVDS,支持ANSI-644电平。AD6642接收机能够对很宽的中频频谱进行数字化处理。各接收机设计用于同步接收不同的天线。该IF采样架构与传统的模拟技术或较低集成度的数字方法相比,能大幅度降低器件的成本和复杂度。

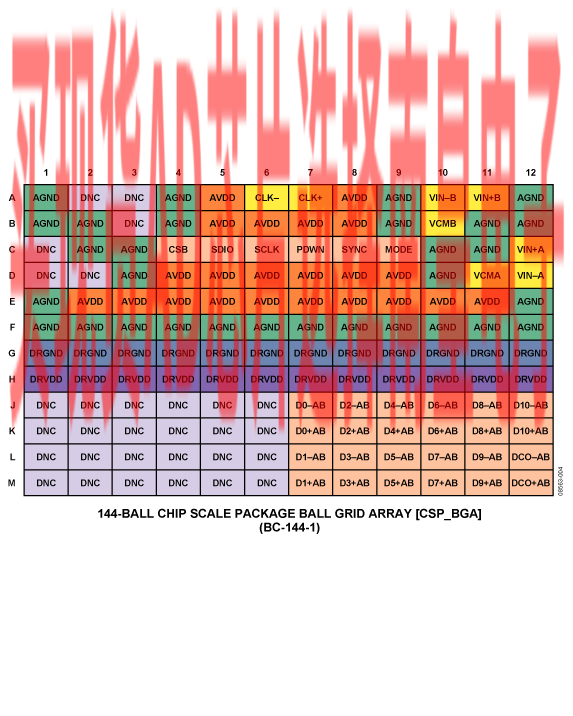

灵活的关断选项可以明显降低功耗。器件设置与控制的编程利用三线式SPI兼容型串行接口来完成;该接口提供多种工作模式,支持电路板级系统测试。AD6642采用144引脚无铅10 mm × 10 mm芯片级球栅阵列(CSP_BGA)封装,符合RoHS标准,额定温度范围为?40°C至+85°C工业温度范围。

应用

- 通信

- 分集无线电和智能天线(MIMO)系统

- 多模式数字接收器(3G)

- WCDMA、LTE、CDMA2000

- WiMAX、TD-SCDMA

- I/Q解调系统

- 通用软件无线电

- 每个通道11位、200 MSPS输出数据速率

- 集成噪声整形再量化器(NSR)

- 使能NSR时的性能

SNR:75.5 dBFS(40 MHz带宽,最高70 MHz,185 MSPS)

SNR: 73.7 dBFS(60 MHz带宽,最高70 MHz,185 MSPS) - 禁用NSR时的性能

SNR:66.5 dBFS(最高70 MHz,185 MSPS)

SFDR: 83 dBc(最高70 MHz,185 MSPS) - 低功耗:0.62 W (185 MSPS)

- 1.8 V模拟电源供电

- 1.8 V LVDS(ANSI-644电平)输出

- 1至8整数时钟分频器

- ADC内部基准电压源

- 模拟输入范围:1.75 V p-p(可编程至2 V p-p)

- 差分模拟输入、800 MHz带宽

- 欲了解更多特性,请参考数据手册

AD6642BBCZ,封装:144-Ball CSPBGA (10mm x 10mm x 1.4mm),包装形式及数量:托盘,184,工作温度:-40 to 85C,AD官网报价:89.23(100-499个);75.85(1000+个)

EVAL-AD6642:AD6642 评估板

本页面提供有关评估AD6642的评估板文档和订购信息。

HSC-ADC-EVALCZ:基于FPGA的数据采集套件

HSC-ADC-EVALCZ高速转换器评估平台使用基于FPGA的缓冲存储器板,采集来自ADI高速模数转换器(ADC)评估板的数字数据块。该板通过USB端口连接到PC,并与VisualAnalog软件配合使用来快速评估高速ADC的性能。该评估套件设置简单。所需的额外设备包括ADI高速ADC评估板、信号源和时钟源。一旦连接该套件并上电,PC便立即开始评估。